# 並列分散リアルタイム処理用 レスポンシブプロセッサ

慶應義塾大学 / 電子技術総合研究所

山崎 信行

E-mail: yamasaki@{ics.keio.ac.jp, etl.go.jp}

<http://www.ny.ics.keio.ac.jp>

# 概要

- ◆ 基礎

- ◆ 並列分散処理 / 制御

- ◆ リアルタイム

- ◆ 応用

- ◆ 並列分散リアルタイム制御用レスポンシブ・プロセッサのアーキテクチャ

- ◆ リアルタイム通信

- ◆ システムオンチップ

- ◆ 開発環境

# 並列分散処理

## 情報通信分野 一般的

- ◆ 様々な分野(科学技術計算、データベース、etc.)で広く一般的に利用されている

## 制御分野 一般的ではない

- ◆ 制御 자체が分散処理に不向きであると考えられている

- ◆ リアルタイム通信の標準がない

- ◆ 共通のプラットホームがない

現状: アドホックに設計・実装

# 並列分散制御

## 集中制御

- ◆ 一極集中のコントローラ(CPU)が全てのI/Oを制御

## 並列分散制御

- ◆ 複数のノードコントローラを結合することによってシステム全体を制御

# 並列制御

- - ◆ 逐次アルゴリズムの制御アルゴリズムを並列化

- ◆ 複数のプロセッサで並列実行

- ◆ 単なる並列処理との相違: 処理に時間制約(実時間性が要求される)

- ↓

- ◆ 通常の並列処理: ある共有データを別プロセッサが参照するのに時間がかかるてもコンシステムしがとれていれば正常に動作

- ◆ 並列制御: ある時間制約以内に参照できなければ安定して制御できない

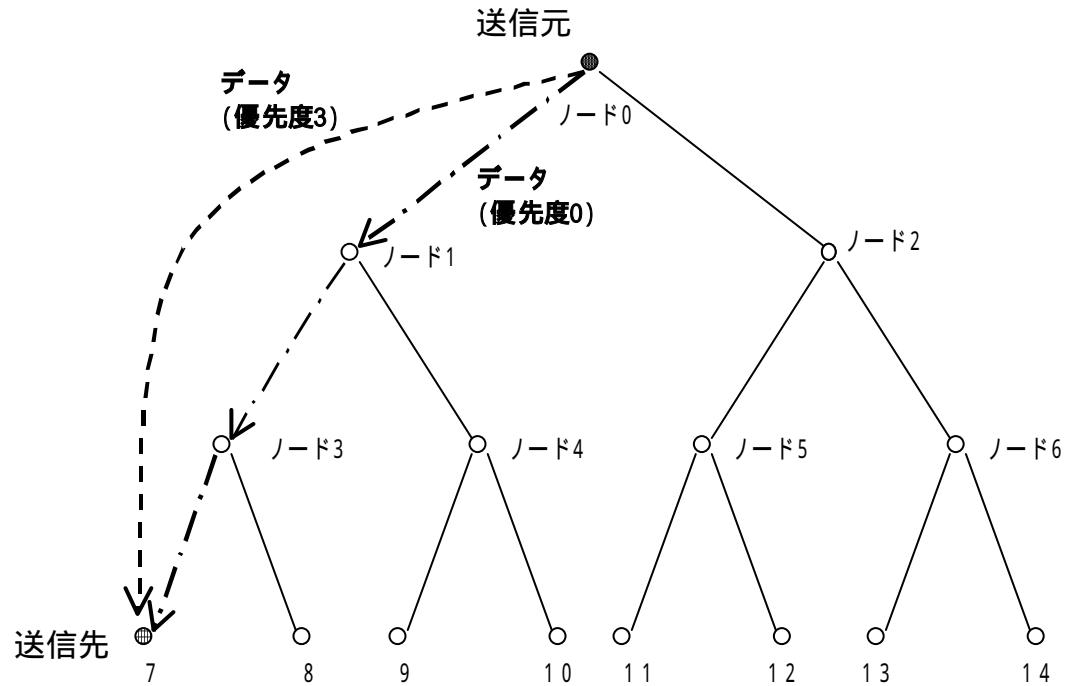

# 分散制御

- ◆ 並列制御との相違点: ひとつの処理(制御アルゴリズム)を分割するわけではない

- ◆ ノードコントローラ: 自身の管理化のI/O(センサ、アクチュエータ等)を独立して制御

- ◆ システム: 複数のノードコントローラから構成

- ◆ ノードコントローラ間で互いに(実時間)通信

- ◆ 階層化 or 完全に平等

# リアルタイム性

- ◆ ある処理の真偽が、その処理の結果だけではなく、その処理の時間にも依存する性質

- ◆ 狹義には、その処理が時間制約(デッドライン)を厳守する性質

# リアルタイム性の種別

- ◆ **ハードリアルタイム**: 必ず時間制約を守る性質(時間制約を破るとシステムに損害を与える可能性)

- ◆ **ソフトリアルタイム**: 時間制約を多少破ることを許容する性質(時間制約を破ってもシステムに損害を与えない)

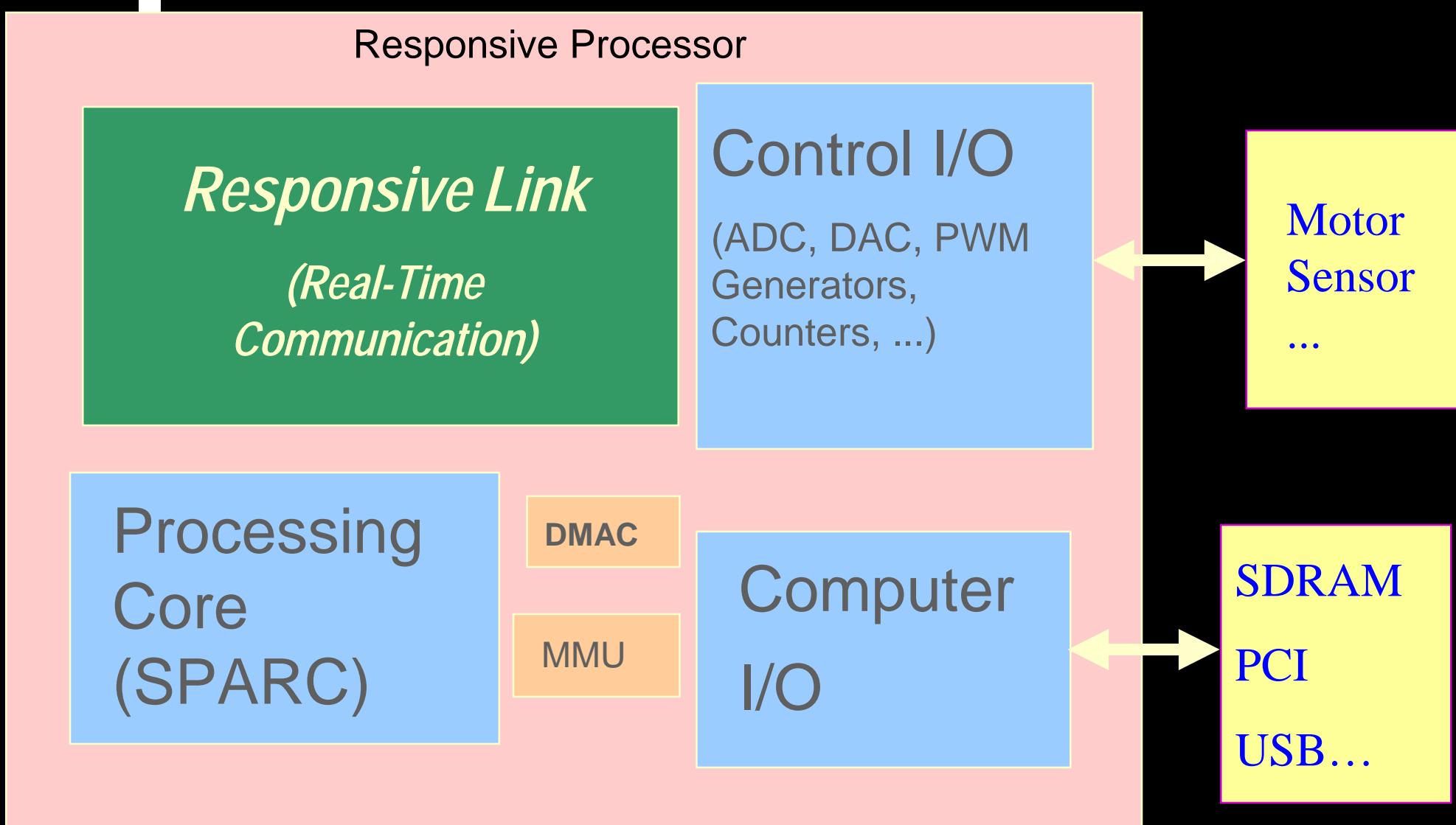

# レスポンシブ・プロセッサの概要

用途■ Home Automation, Factory Automation, 各種ロボット等の

様々な並列分散リアルタイム制御

- ◆ プロセッシングコア(SPARC)

- ◆ レスポンシブ・リンク(リアルタイム通信)

- ◆ コンピュータ用周辺(SDRAM I/F, DMAC, PCI, USB, Timers/Counters, SIO, PIO, ...)

- ◆ 制御用周辺(ADC, DAC, PWM Generators, Pulse Counters, ...)

並列分散リアルタイム制御に必要な機能を1チップに集積

System-on-a-chip

任意のトポロジで複数結合

様々な制御システムを容易に構築可能に

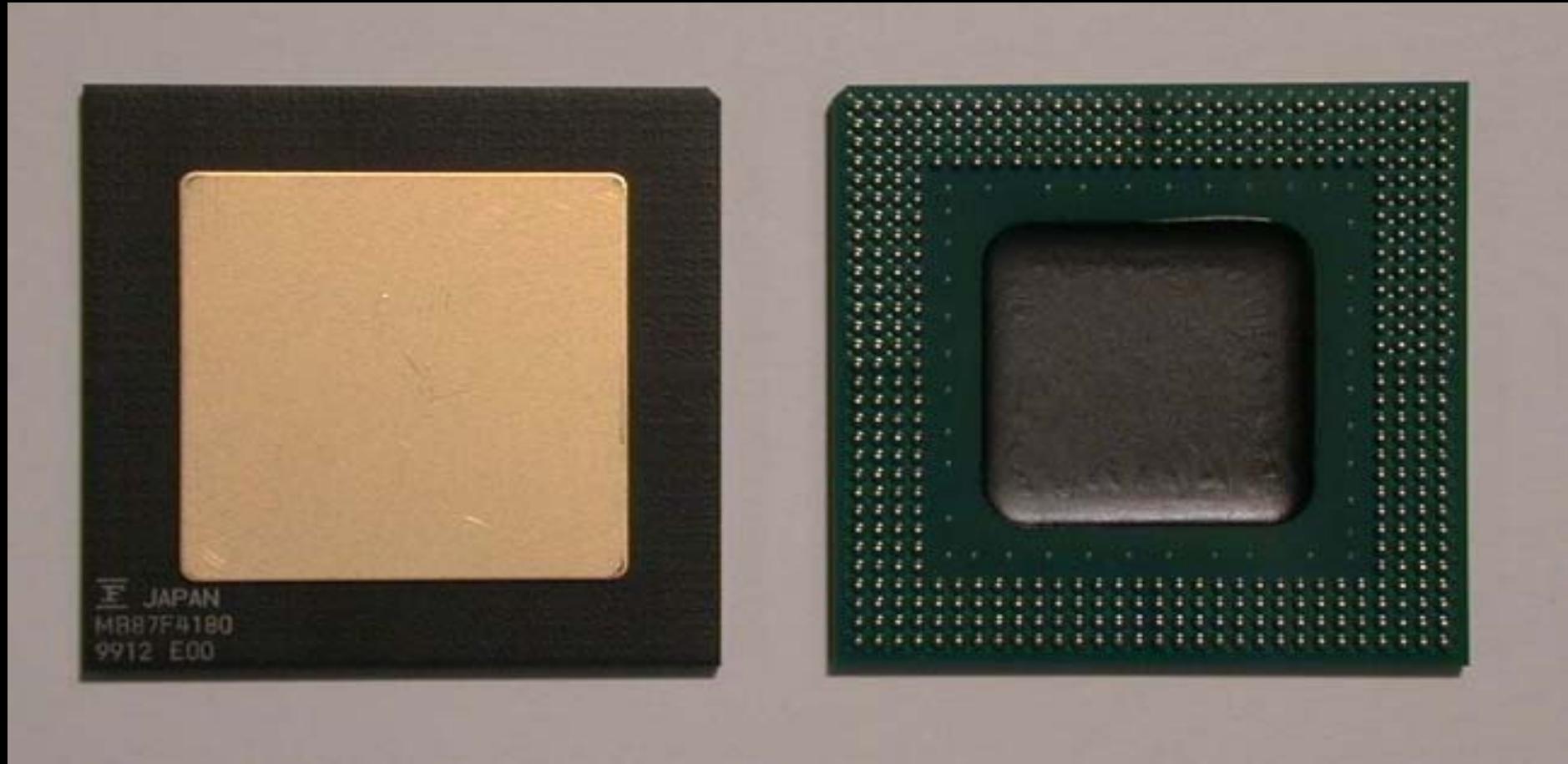

# レスポンシブプロセッサの概観

■

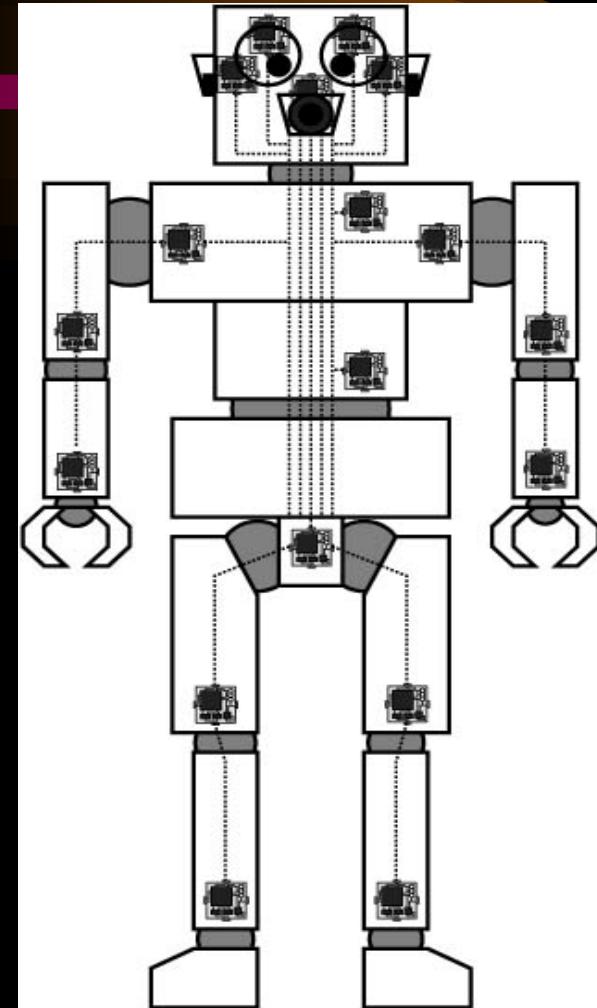

# アプリケーション

- ◆ ホームオートメーション

- ◆ オフィスオートメーション

- ◆ ファクトリーオートメーション

- ◆ 各種ロボット

- ◆ 自動車

- ◆ インテリジェントビルディング

- ◆ アミューズメントシステム 等

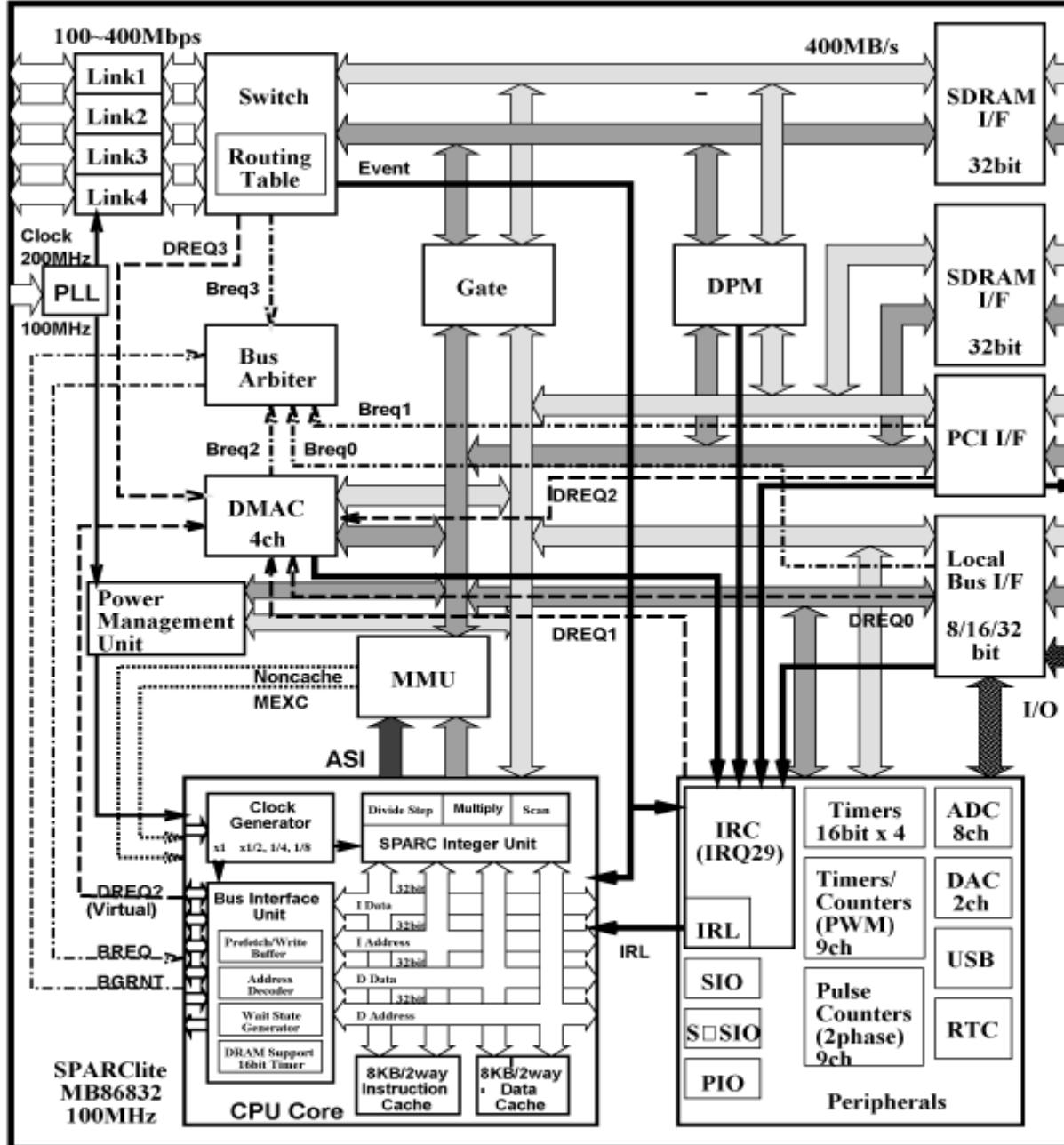

# ブロックダイアグラム

# 従来の実時間通信規格

- - ◆ IEEE-1394

- ◆ USB

- ◆ ソフトリアルタイム(アイソクロナス転送)

- ◆ アイソクロナスモードでのエラー処理なし

- ◆ 集中制御: 低いロバスト性

- ◆ 最大ノード数が少ない(IEEE-1394:63, USB: 127)

- ◆ トポロジーが固定(木構造)

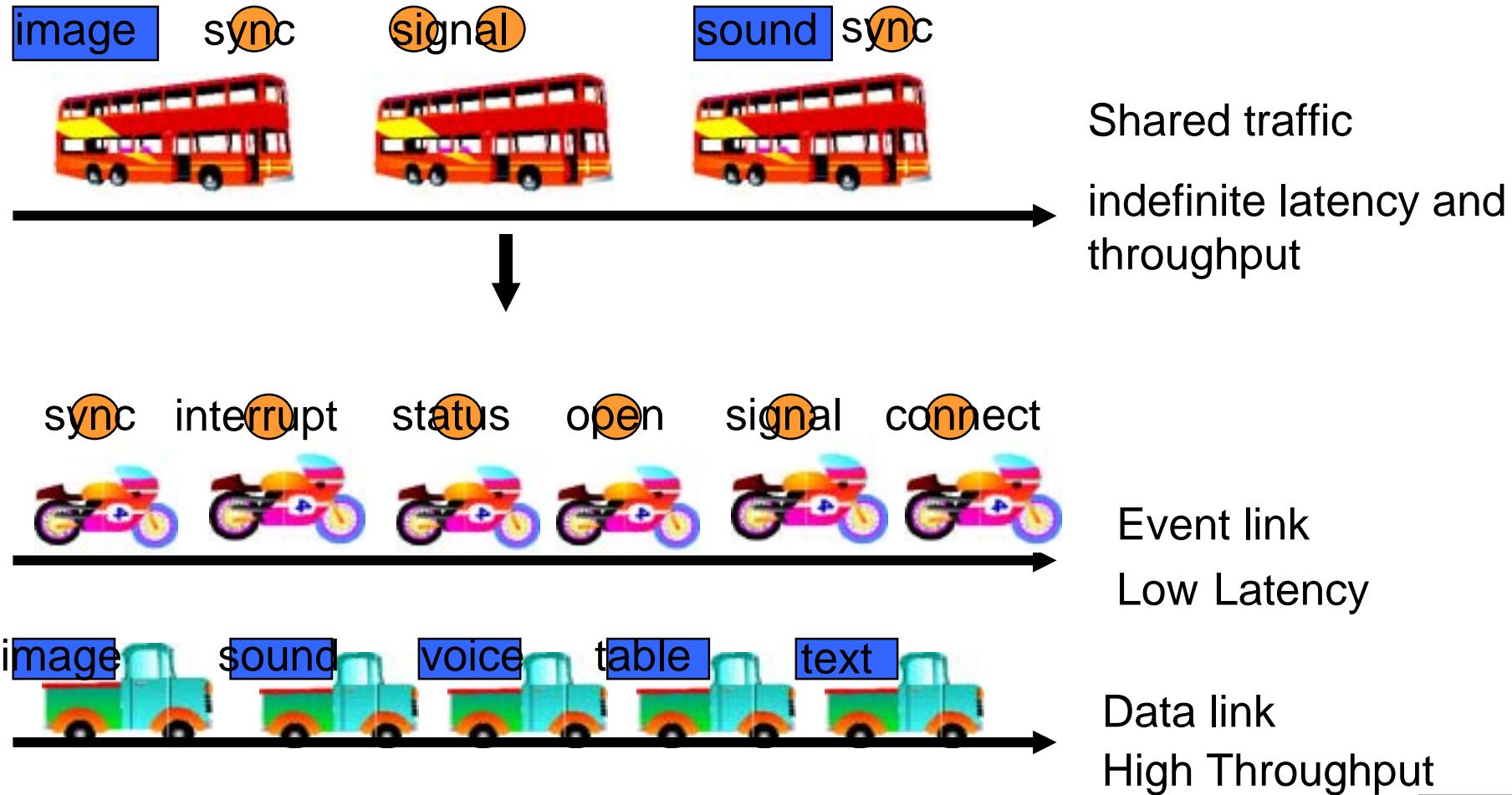

# リアルタイム通信におけるトレードオフ

- ◆ ソフトリアルタイム通信: バンド幅保証

→ スループットを上げたい

- ◆ ハードリアルタイム通信: レイテンシ保証

→ レイテンシを小さくしたい

|         |   |   |

|---------|---|---|

| パケットサイズ | 大 | 小 |

| スループット  | 大 | 小 |

| レイテンシ   | 大 | 小 |

# レスポンシブ・リンク (リアルタイム通信)

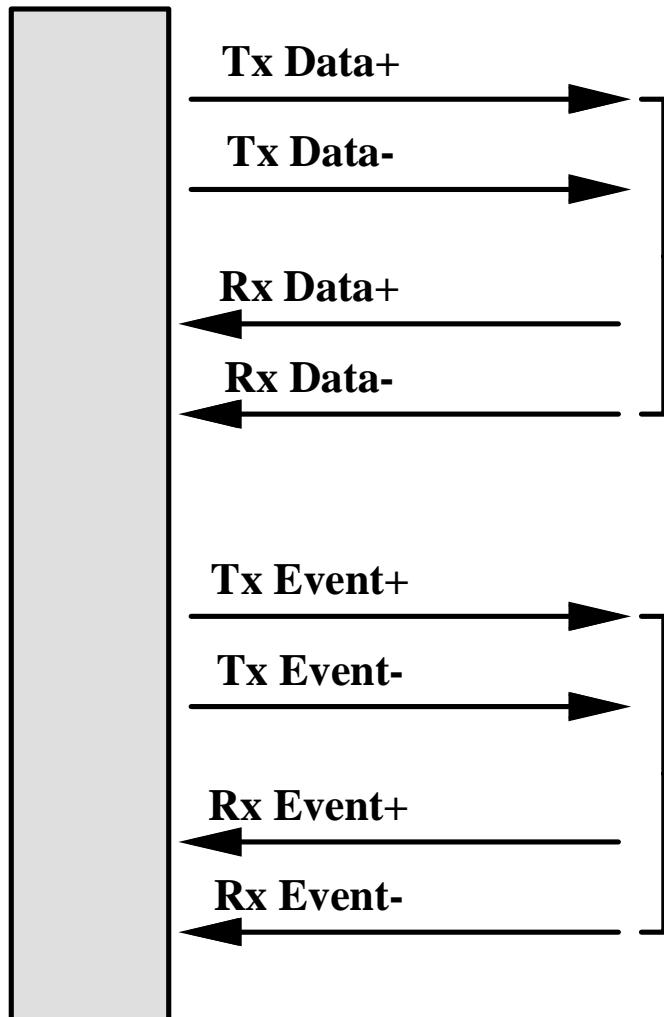

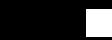

- ◆ データとイベントの分離

- ◆ 固定パケットサイズ: 64Bデータ, 16Bイベント

- ◆ フルデュプレックス差動型インターフェース

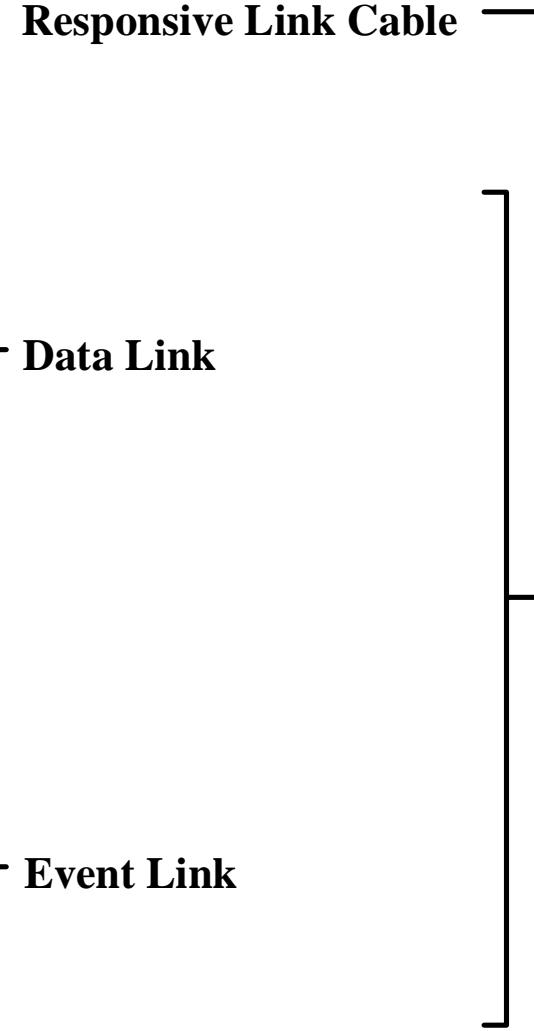

- ◆ ハードウェアルーティング

- ◆ データとイベントの独立したルーティング

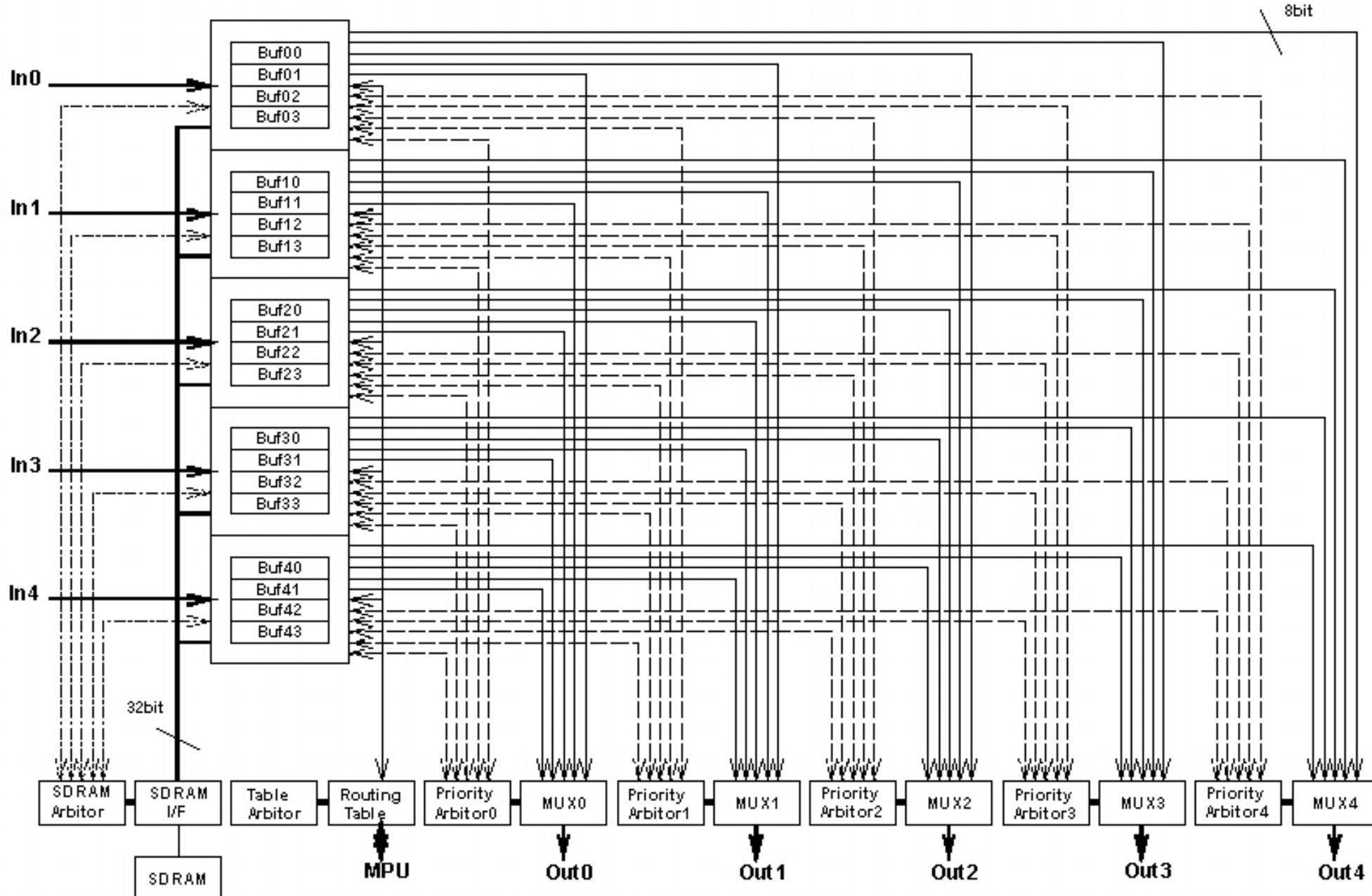

- ◆ 追越機能付ネットワークスイッチ (高い優先度のパケットがノード毎に低い優先度のパケットを追越)

- ◆ 優先度の付け替え (パケットの優先度はノード毎に新優先度に付け替え可能)

- ◆ 同じネットワークアドレスを持つパケットの経路を優先度によって別々に設定及び変更可能(専用回線や迂回路の実現)

- ◆ 前方エラー訂正

- ◆ リンク速度可変 (12.5 to 100M bps)

- ◆ トポロジーフリー

- ◆ Point-to-point

Responsive

Processor

# イベントとデータの分離

# データリンク

用途: バンド幅保証によるソフトリアルタイム通信の実現

- ◆通常のデータ転送

- ◆動画・音声などのマルチメディアデータの転送

- ◆スループット重視

-

- ◆ 優先度によりノードごとにパケットの追越

- ◆ Point-to-point

- ◆ パケットサイズ: 比較的大(固定(64B))

# イベントリンク

用途: レイテンシ保証のハードリアルタイム転送

- ◆ プロセッサ間割り込み

- ◆ プロセッサ間同期

- ◆ プロセッサ間ステータス転送

- ◆ レイテンシ重視

-

- ◆ Point-to-point

- ◆ パケットサイズ: 小さく固定(16B)

- ◆ データパスとイベントパスが分離

- ◆ イベントパケットの量: 普通のデータと比較して非常に少ない

- ◆ 優先度によりノードごとにパケットの追越可能

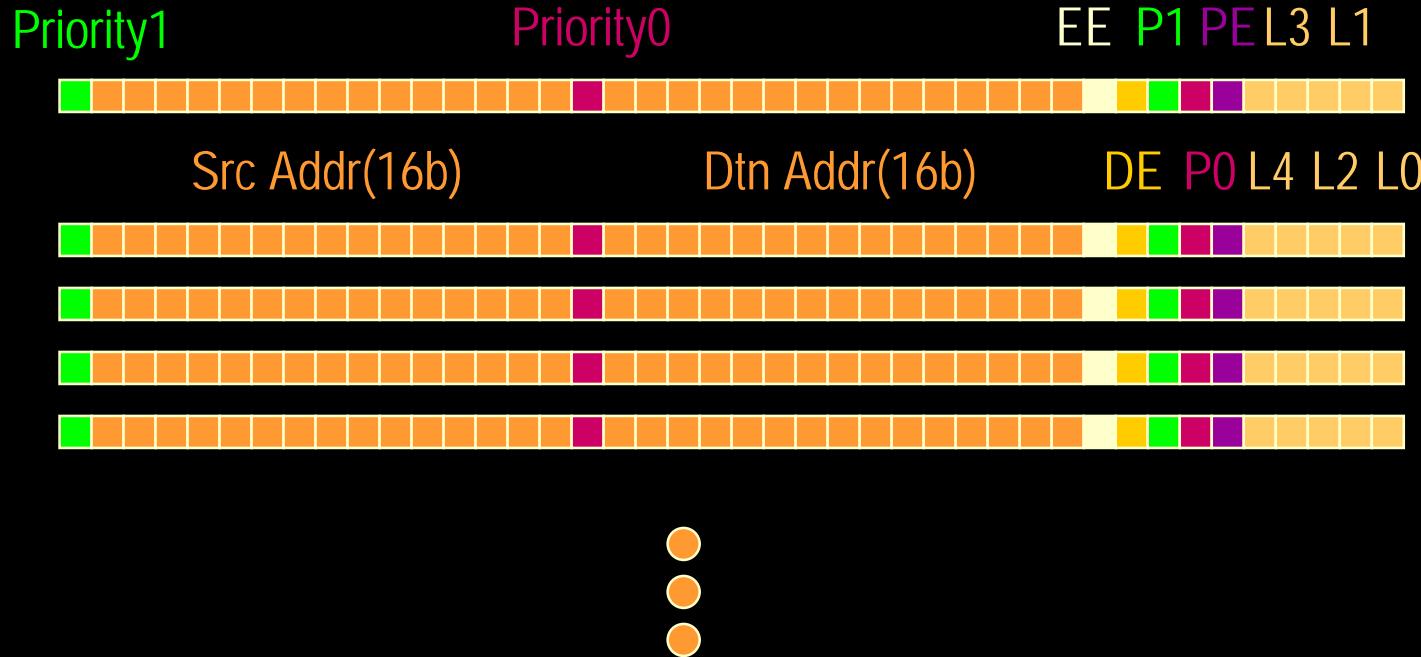

# パケット フォーマット

## Data Packet Format (64B)

## Event Packet Format (16B)

| <i>Source Addr.</i> | <i>Destination Addr.</i>    |

|---------------------|-----------------------------|

|                     | <i>Payload</i>              |

|                     | <i>Control &amp; Status</i> |

**1 byte**

## **Control & Status Format (32bits)**

|              |          |               |               |                |                |                    |                |                |                |

|--------------|----------|---------------|---------------|----------------|----------------|--------------------|----------------|----------------|----------------|

| <b>1 bit</b> | <b>0</b> | <i>0</i>      | <i>Full</i>   |                |                | <i>Data Length</i> |                |                |                |

|              | <b>1</b> | <i>Dirty0</i> | <i>Dirty1</i> | <i>Dirty2</i>  | <i>Dirty3</i>  | <i>Dirty4</i>      | <i>Dirty5</i>  | <i>Dirty6</i>  | <i>Dirty7</i>  |

|              | <b>2</b> | <i>Dirty8</i> | <i>Dirty9</i> | <i>Dirty10</i> | <i>Dirty11</i> | <i>Dirty12</i>     | <i>Dirty13</i> | <i>Dirty14</i> | <i>Dirty15</i> |

|              | <b>3</b> | <i>Start</i>  | <i>End</i>    | <i>Int.</i>    | <i>Fatal</i>   | <i>Correct</i>     | <i>Serial</i>  | <i>Number</i>  | (Cnt.)         |

## Frame Format (12bits)

*Data bits*      *Redundancy bits*

# レスポンシブリンクインターフェース

Responsive Link Connector

Responsive Link Cable

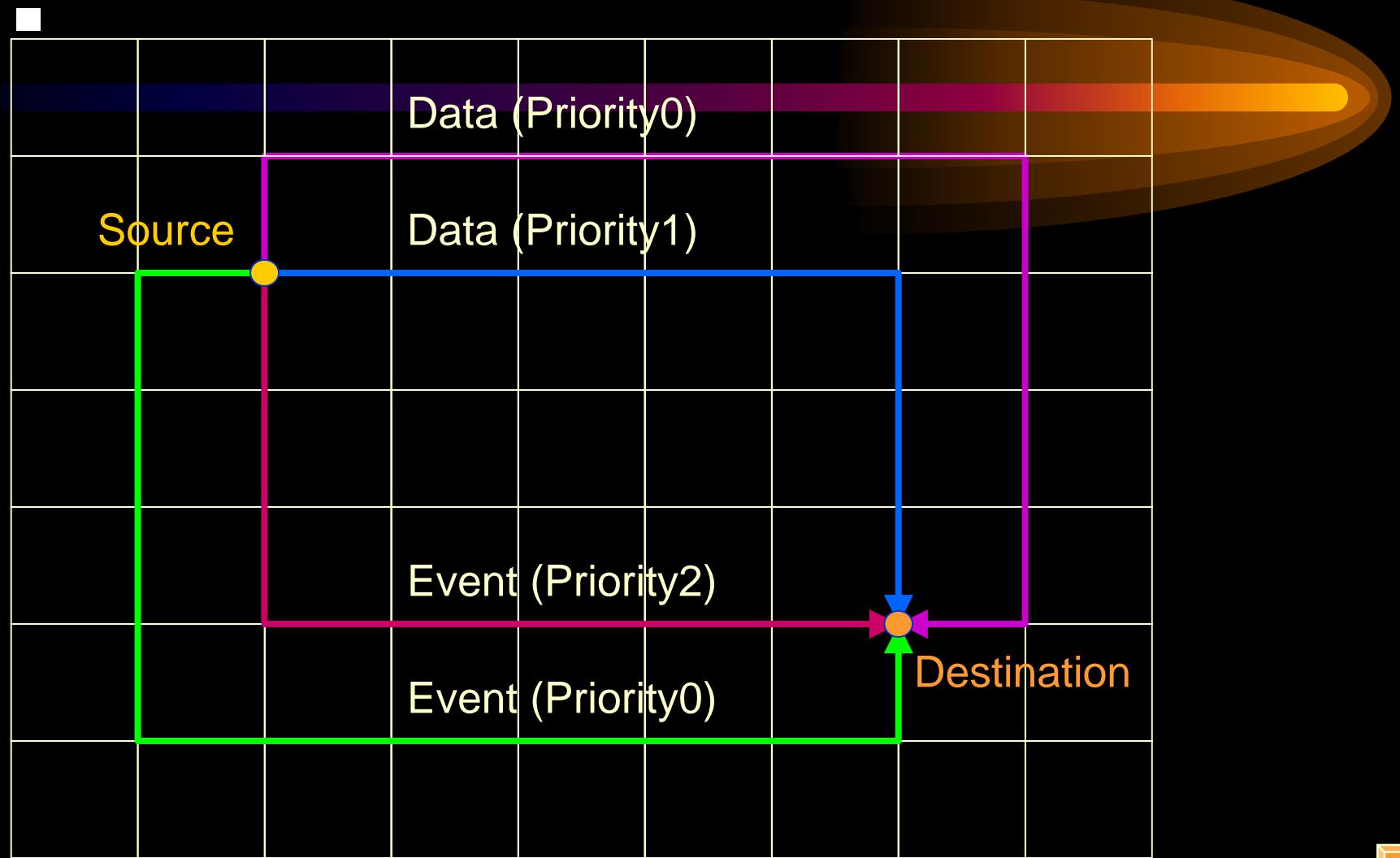

# 追越機能付ネットワークスイッチ

# 追越バッファの制御

# ルーティングテーブル

- ◆同じソースとデスティネーションでもプライオリティごとに異なる経路設定が可能(デフォルトルートはプライオリティ0)

- ◆ノードごとにプライオリティの付け替えが可能

# 優先度に応じたルーティング

# 優先度によるルーティング

# 低レベル・データ／イベント通信

- ◆ Forward Error Correction(FEC)

- ◆ 巡回ハミング符号

- ◆ 8bitデータ + 4bit冗長符号

- ◆ Bit stuffing

- ◆ NRZI(Non Return to Zero Inverted)

- ◆ DPLL(Digital Phase-Lock-Loop)

- ◆ 同期フレーム(Setup Pattern)

- ◆ リンク速度可変: サンプリング数可変(100Mbaud, 50Mbaud, 25Mbaud, 12.5Mbaud)

- ◆ 信号インターフェース:P-CML(LVTTL, ECL), LVDS

# 前方エラー訂正

- ◆レイテンシを低く抑えるためにbyte単位でエラー訂正

- ◆1byte(8bit)のバイト列を1frame(12bit)へ変換(8bitの情報ビット列に誤り訂正用の4bitの冗長ビット列)

- ◆ハミング符号

- ◆生成多項式:  $x^4+x+1$

# *Bit Stuffing*

転送データ中に5つの連續した1:その後ろに0を挿入

- ◆直流成分発生の回避

- ◆受信側のピット同期への支障回避

# *NRZI (Non Return to Zero Inverted)*

- ◆0を送信時: データビットを反転

- ◆1を送信時: データビットを維持

# レスポンシブプロセッサに必要な機能

- ◆ ロボット関係や制御関係のマーリングリストを用いてアンケートを実施

- ◆ 必要な機能、開発環境、OS等を絞り込み

# レスポンシブプロセッサの機能

- ◆ Processing Core (SPARClite MB86832 100MHz)

- ◆ Power Management Unit (100, 80, 60, 40, 20 [MHz], Sleep)

- ◆ MMU (64way)

- ◆ Responsive Links (4 links, 200, 100, 50, 25 [MHz])

- ◆ DMAC (4channels, Bus swapping, Bus sizing)

- ◆ SDRAM I/F (2channels, 100MHz)

- ◆ PCI I/F (Master/Target)

- ◆ USB I/F (Function, Hub)

- ◆ PWM Generators (50MHz, 9channels)

- ◆ Pulse Counters (24bit, 9channels)

- ◆ Timers/Counters (16bit, 4channels)

- ◆ Real-Time Clock

- ◆ A/D Converters (10bit, 8channels)

- ◆ D/A Converters (8bit, 2channels)

- ◆ Interrupt Controllers (43channels)

- ◆ SIO (RS-232C, 2channels)

- ◆ PIO (16bit), ...

# レスポンシブ プロセッサの ダイアグラム

Data

Interrupt

Address

Control

# デザインルール

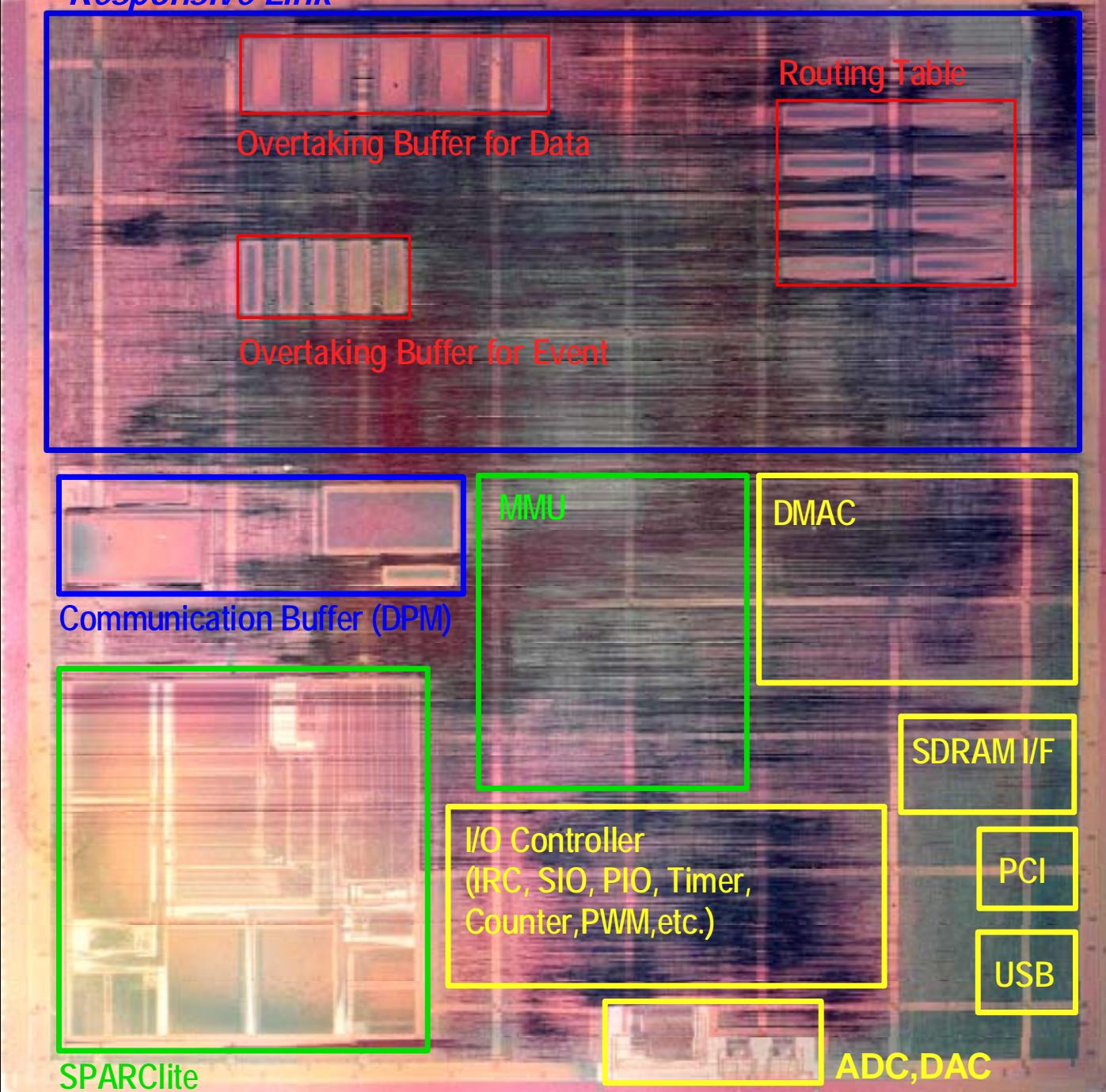

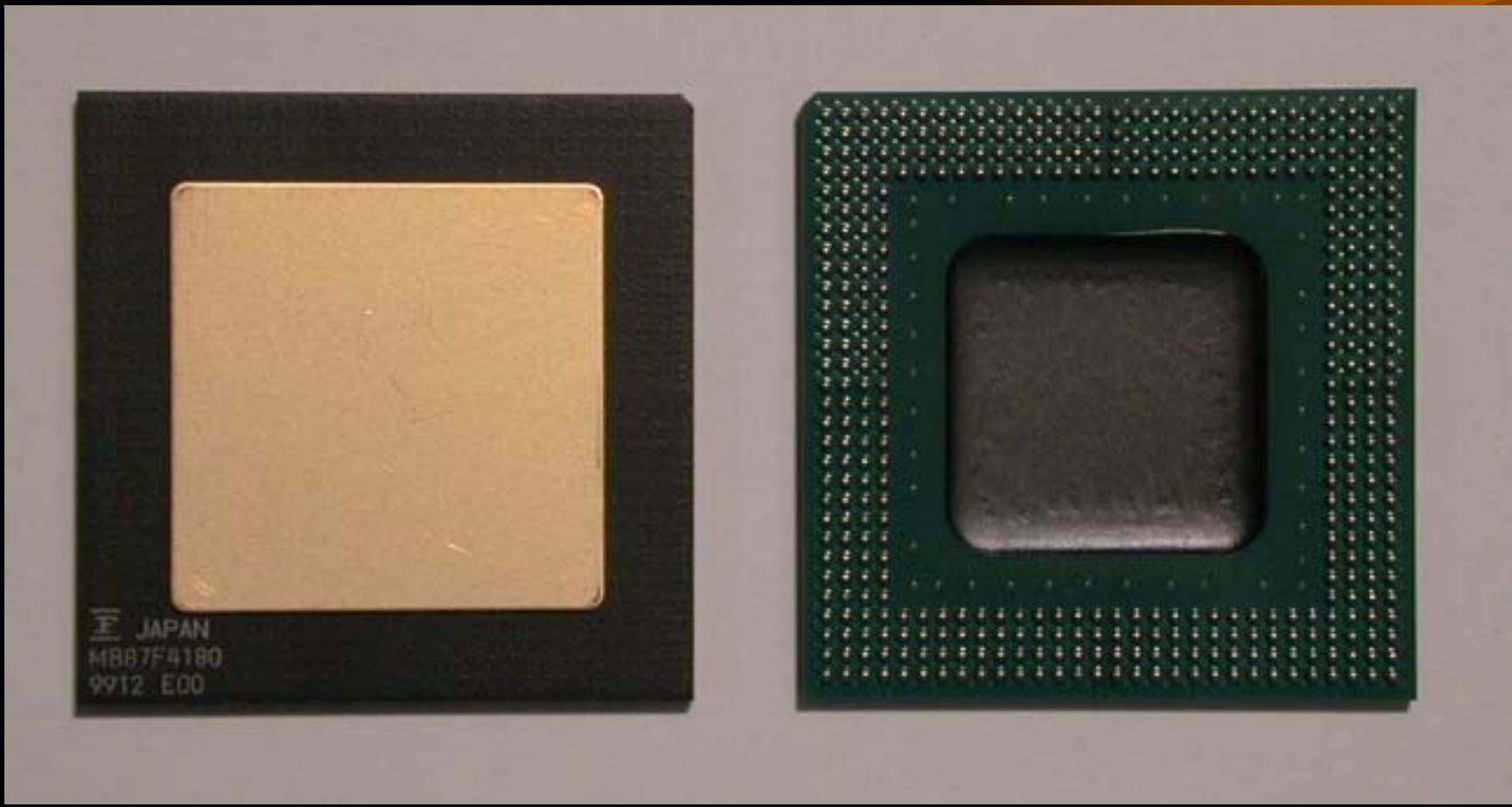

- ◆ Process : 0.35 μ m, CMOS, 4 layered metal

- ◆ Usable gates : 2,378 k gates

- ◆ Die size : 14.5 mm x 14.5mm = 210mm<sup>2</sup>

- ◆ Package : 416pin BGA (40mm x 40mm)

- ◆ Voltage : 3.3V

- ◆ Max. power : 2W

## Responsive Link

### レイアウト

# レスポンシブプロセッサの概観

# 速度と消費電力

## ■ Performance of MPU

| <i>Clock(MHz)</i>  | 100 | 80  | 60  | 40  | 20  | Sleep |

|--------------------|-----|-----|-----|-----|-----|-------|

| <i>Speed(MIPS)</i> | 121 | 97  | 73  | 48  | 24  | 0     |

| <i>Power(W)</i>    | 1.0 | 0.8 | 0.6 | 0.4 | 0.2 | 0.01  |

## Performance of Responsive Link

| <i>Clock (MHz)</i>              | 200 | 100 | 50   | 25   |

|---------------------------------|-----|-----|------|------|

| <i>Max. Speed (Mbaud)</i>       | 100 | 50  | 25   | 12.5 |

| <i>Speed of Data (Mbps)</i>     | 67  | 33  | 17   | 8    |

| <i>Latency of Event( μ sec)</i> | 3.1 | 6.2 | 12.5 | 25   |

| <i>Power (W)</i>                | 0.2 | 0.1 | 0.05 | 0.02 |

$$\text{Latency of Event (Worst)} = 1 \text{ ( } \mu \text{ sec)} + 2 \text{ ( } \mu \text{ sec/hop) } \times n \text{ (hop)}$$

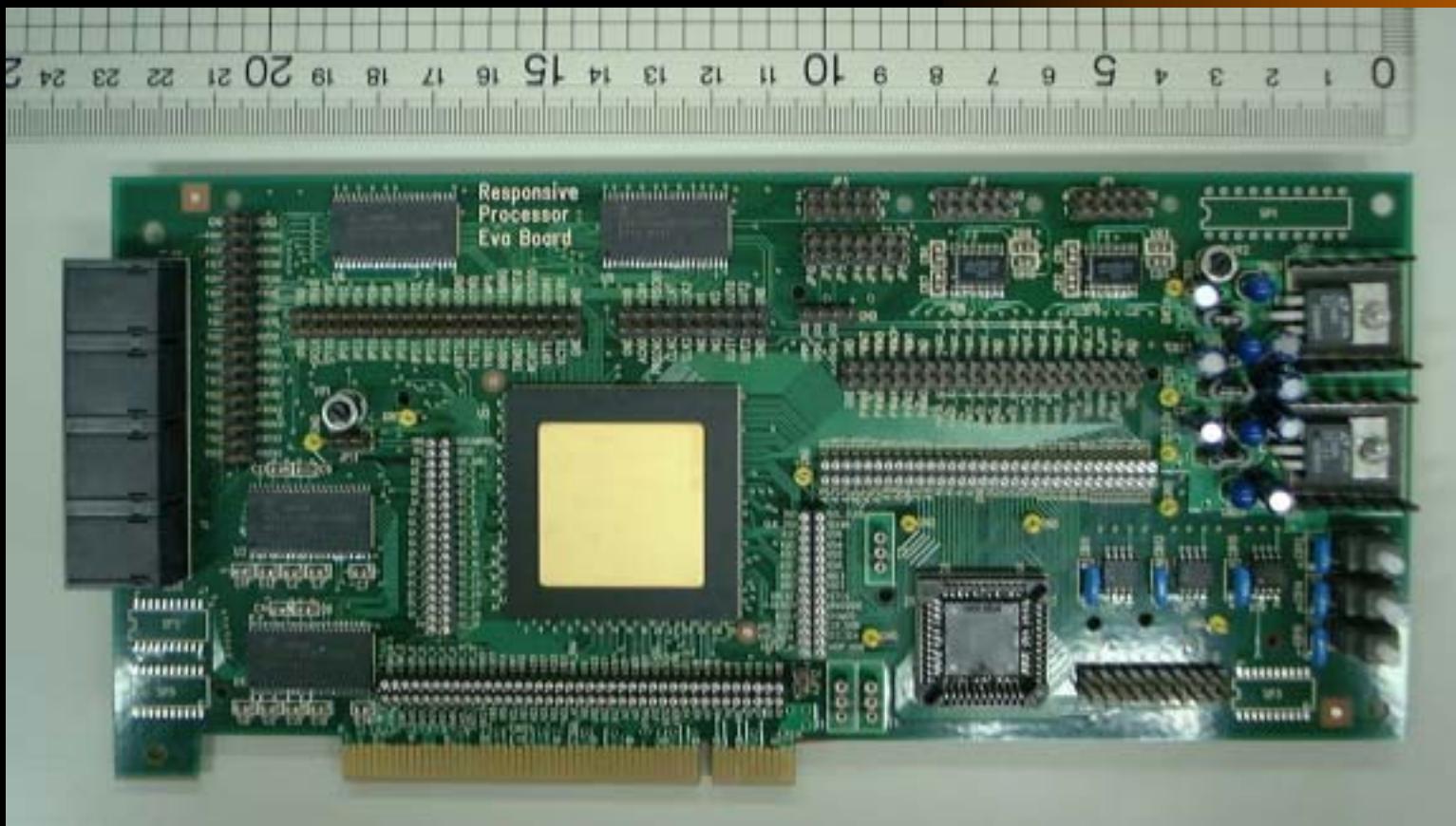

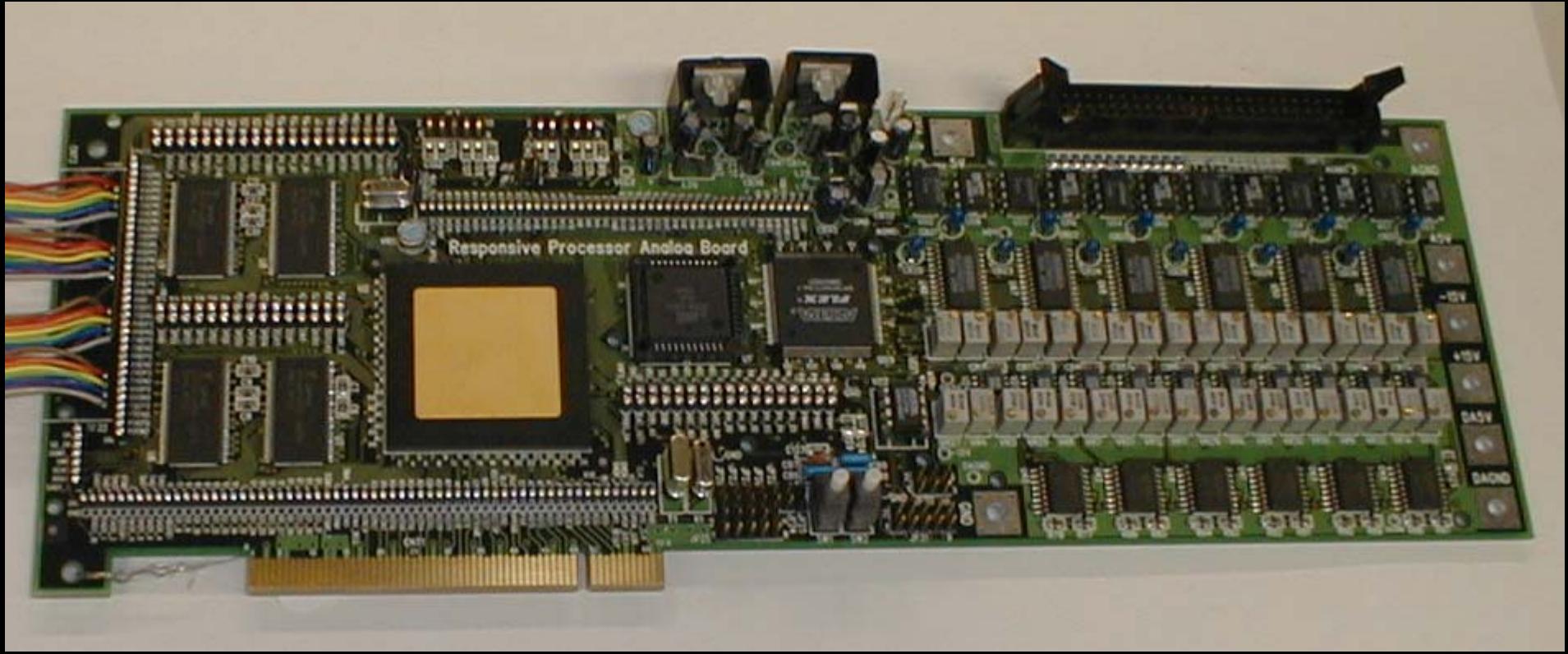

# 開発用ボード

- ◆ PCI card (PCI half size)

- ◆ CardBus card (PCMCIA size)

- ◆ Embedded board (Credit card size)

# PCI Card

# *PCI Card with Analog Devices*

- ◆ 16bit DAC 6channels

- ◆ 12bit ADC 6channels

# 開発環境

- ◆ PC(Windows or UNIX)とPCI,USB,RS-232C等で接続してクロス開発

- ◆ GNUベースのクロス開発ツール (gcc, as, ld, make, etc.)

- ◆ WinGDB等によるソースレベルデバッグ

**gdb sparclite** - WinGDB

File Edit Window Debug Help

Source 1

mon.c

```

volatile unsigned long *ptr;

int i, j;

char buf[BUFSIZ];

char *token;

ASI4put(0x03010000, 0xFFFFF000) ;

while( 1 ) {

printf( "MON>" );

if( !fgets( buf, BUFSIZ, stdin ) )

break;

edit( buf );

if( !(token = strtok( buf, " \t\n" ))

usage( "mon" );

continue;

}

type = *token;

if( !(token = strtok( NULL,

usage( "mon" );

continue;

}

printf( "MON>" );

if( !fgets( buf, BUFSIZ, st

break;

edit( buf );

if( !(token = strtok( buf,

usage( "mon" );

```

Reg1

|      |          |                     |          |

|------|----------|---------------------|----------|

| g0   | 00000000 | 1FFFFFFF            | 0000000A |

| g4   | 00000A00 | 02080000            | 02000000 |

| o0   | 03010000 | FFFFF000            | FFFF6000 |

| o4   | FFFFFFFF | FFFFFFFF            | 0207F8A8 |

| l0   | 00000010 | 020165BC            | 020165C0 |

| l4   | 02016B00 | 0201A989            | 0201B000 |

| i0   | 0201A848 | 02019400            | FFFFFFFF |

| i4   | FFFFFFFF | FFFFFFFF            | 0207FD30 |

| y    | 00000000 | 0F000FC0            | 00000004 |

| pc   | 020102A0 | 020102A4            | 00000000 |

| dda1 | 00000000 | 00000000            | 00000000 |

| dcr  | 00000000 | 00000003            |          |

| PC   | 020102A0 | 0x20102a0 <main+44> |          |

| nscr | 0E000FC0 |                     |          |

Command Log1

```

(gdb)

(gdb) break main

Note: breakpoint 1 also set at pc 0x2010280.

Breakpoint 2 at 0x2010280: file mon.c, line 40.

(gdb) j main

Continuing at 0x2010280.

Breakpoint 1, main () at mon.c:40

40          ASI4put(0x03010000, 0xFFFFF000) ;

(gdb) step

42          while( 1 ) {

(gdb) next

43          printf( "MON>" );

(gdb) |

```

# オペレーティングシステム

## 商用

- ◆ VxWorks

- ◆ pSOSystem

- ◆  $\mu$ iTRON

- ◆ OS-9

## 研究用

- ◆ RT-Mach

- ◆  $\mu$ *PULSER*

- ◆ RT-Linux

# *Responsive Link* の標準化(国外)

ISO/IEC JTC1 SC25にて標準化作業中

- ◆99年度のISO/IEC JTC1 SC25国際会議(ベルリン)にて*Responsive Link*のNWIP承認済

- ◆ANSI標準化検討中

# *Responsive Link の標準化(国内)*

■ JTC1 SC25 WG4 *Responsive Link SG*

にて詳細仕様作成作業中

*Responsive Link SG* 参加企業：松下電器（株）、三菱電機（株）、富士通（株）、（株）日立製作所、（株）半導体理工学研究センター、電子技術総合研究所、慶應義塾大学、九州大学

JTC1 SC25 WG4 参加企業：RWCP、NTT、沖電気工業（株）、横河電機（株）、三菱電機（株）、富士通（株）、松下通信工業（株）、（株）東芝、（株）日立製作所、ソニー（株）、日本電気（株）、電子技術総合研究所、日本ユニシス（株）、（株）ピクターデータシステムズ、（財）日本規格協会、住友電気工業（株）

# *Responsive Processor* のまとめ

## 並列・分散制御用レスポンシブ・プロセッサ

- ◆ *Responsive Link*

- ◆ Processing Core (SPARC)

- ◆ コンピュータ用周辺

- ◆ 制御用周辺

チップ間をリンクで接続するだけでシステムの柔軟な構成が可能

# まとめ

- - ◆ 基礎

- ◆ 並列分散処理 / 制御

- ◆ リアルタイム性

- ◆ 応用

- ◆ 並列分散リアルタイム制御用レスポンシブ・プロセッサのアーキテクチャ

- ◆ リアルタイム通信

- ◆ システムオンチップ

- ◆ 開発環境